- NUCLEO BOARD WITHOUT MORPHO HEADER PINS SERIAL

- NUCLEO BOARD WITHOUT MORPHO HEADER PINS FULL

- NUCLEO BOARD WITHOUT MORPHO HEADER PINS SOFTWARE

- NUCLEO BOARD WITHOUT MORPHO HEADER PINS CODE

NUCLEO BOARD WITHOUT MORPHO HEADER PINS SOFTWARE

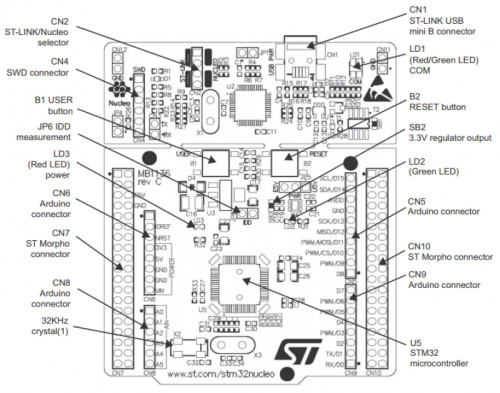

Comprehensive free software libraries and examples available with the STM32Cube MCU Package.On-board ST-LINK debugger/programmer with USB re-enumeration capability: mass storage, Virtual COM port and debug port.Flexible power-supply options: ST-LINK, USB VBUS, or external sources.

NUCLEO BOARD WITHOUT MORPHO HEADER PINS FULL

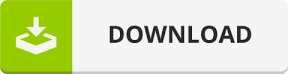

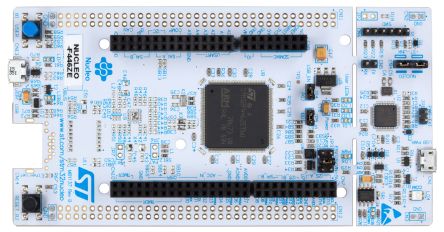

Board connectors:ARDUINO® Uno V3 expansion connectorST morpho extension pin headers for full access to all STM32 I/Os.STM32 microcontroller in LQFP64 package.

NUCLEO BOARD WITHOUT MORPHO HEADER PINS SERIAL

Development support: serial wire debug (SWD), JTAG, Embedded Trace Macrocell™.USB Type-C™ /USB power delivery controller (UCPD).USB 2.0 full-speed interface with LPM and BCD support.4 x SPIs, 4 to 16 programmable bit frames, 2 x with multiplexed half duplex I2S interface.5 x USART/UARTs (ISO 7816 interface, LIN, IrDA, modem control).4 x I2C Fast mode plus (1 Mbit/s) with 20 mA current sink, SMBus/PMBus, wakeup from stop.3 x FDCAN controller supporting flexible data rate.Calendar RTC with alarm, periodic wakeup from stop/standby.2 x watchdog timers (independent, window).2 x 16-bit timers with IC/OC/OCN/PWM, dead time generation and emergency stop.1 x 16-bit timer with 2 x IC/OCs, one OCN/PWM, dead time generation and emergency stop.3 x 16-bit 8-channel advanced motor control timers, with up to 8 x PWM channels, dead time generation and emergency stop.2 x 32-bit timer and 2 x 16-bit timers with up to four IC/OC/PWM or pulse counter and quadrature (incremental) encoder input.HRTIM (Hi-Resolution and complex waveform builder): 6 x16-bit counters, 184 ps resolution, 12 PWM.Internal voltage reference buffer (VREFBUF) supporting three output voltages (2.048 V, 2.5 V, 2.95 V).6 x operational amplifiers that can be used in PGA mode, all terminals accessible.7 x ultra-fast rail-to-rail analog comparators.4 x unbuffered internal channels 15 MSPS.Resolution up to 16-bit with hardware oversampling, 0 to 3.6 V conversion range 5 x 12-bit ADCs 0.25 µs, up to 42 channels.Several I/Os with 5 V tolerant capability.All mappable on external interrupt vectors.Internal 16 MHz RC with PLL option (± 1%).

VBAT supply for RTC and backup registers.Low-power modes: sleep, stop, standby and shutdown.Power-on/power-down reset (POR/PDR/BOR).External memory interface for static memories FSMC supporting SRAM, PSRAM, NOR and NAND memories.Routine booster: 32 Kbytes of SRAM on instruction and data bus, with hardware parity check (CCM SRAM).96 Kbytes of SRAM, with hardware parity check implemented on the first 32 Kbytes.

NUCLEO BOARD WITHOUT MORPHO HEADER PINS CODE

0 kommentar(er)

0 kommentar(er)